Alphawave Semi a global leader in high-speed connectivity and compute silicon for the world’s technology infrastructure, has unveiled the availability of the industry’s first 3nm silicon-proven Universal Chiplet Interconnect Express (UCIe) Die-to-Die (D2D) IP subsystem, built on TSMC’s Chip-on-Wafer-on-Substrate (CoWoS) advanced packaging technology.

This complete PHY and controller subsystem, developed in close collaboration with TSMC, is tailored for high-demand applications such as hyperscale data centers, high-performance computing (HPC), and AI. Utilizing TSMC’s CoWoS 2.5D silicon-interposer-based packaging, the fully integrated and highly configurable subsystem delivers a high bandwidth density of 8 Tbps/mm while optimizing I/O complexity, power efficiency, and latency.

The subsystem supports multiple industry protocols—including PCIe, CXL, AXI-4, AXI-S, CXS, and CHI—ensuring interoperability across the growing chiplet ecosystem. Additionally, it features live per-lane health monitoring to boost system robustness and operates at speeds of 24 Gbps to meet the bandwidth needs of advanced D2D connectivity.

This UCIe IP subsystem is now available following extensive characterization of the silicon received from TSMC. Alphawave Semi’s team has rigorously validated it against UCIe standards and specifications, across various process conditions (typical, slow, and fast), and under the targeted voltage and temperature conditions.

The successful validation of D2D link margin, TXIO, and RXIO loopback margins reinforces the readiness of Alphawave Semi’s UCIe IP subsystem for integration into customer SoC designs, supporting next-generation HPC and AI applications.

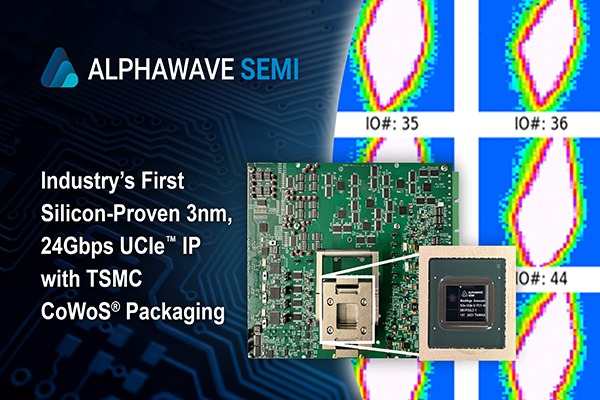

Figure: Alphawave Silicon Validation Setup for UCIe IP Subsystem.

“Achieving successful silicon validation of 3nm 24 Gbps UCIe subsystem with TSMC’s advanced packaging is a significant milestone for Alphawave Semi and underscores the company’s expertise in utilizing the TSMC 3DFabric ecosystem to deliver top-tier connectivity solutions,” said Mohit Gupta, Alphawave Semi’s SVP and GM, Custom Silicon and IP.

Gupta also stated the IP sets “a new benchmark in high-performance connectivity solutions.”

“Our recent collaboration with Alphawave Semi exemplifies how we collaborate with our Open Innovation Platform (OIP) ecosystem partners to enable significant advancements in packaging, meeting the increasing demands in AI and HPC applications,”said Dan Kochpatcharin, Head of Ecosystem and Alliance Management Division at TSMC. “We will continue our partnership with Alphawave Semi to advance the 3D IC design ecosystem to empower faster and power-efficient semiconductor designs.”

Alphawave Semi’s UCIe IP subsystem complies with the latest UCIe Specification Rev 2.0 and includes comprehensive testability and debug features such as JTAG, BIST, DFT, and Known Good Die (KGD) capabilities.