Renesas Electronics, a leading semiconductor provider, has introduced three new System-on-Chip (SoC) technologies designed for automotive multi-domain electronic control units (ECUs). These SoCs incorporate advanced AI processing and chiplet functionality, forming the foundation for next-generation automotive electrical/electronic (E/E) architectures. The company showcased these developments at the International Solid-State Circuits Conference 2026 (ISSCC 2026) in San Francisco, held from February 15–19.

As vehicles transition to software-defined models, automotive SoCs must deliver high performance to run multiple applications simultaneously while supporting scalable chiplet designs. They also need to meet stringent functional safety standards. As multi-domain SoCs become larger and more complex, ensuring automotive-grade reliability becomes increasingly challenging. Higher performance often comes with increased power consumption, making energy efficiency and safety enhancements critical. To address these demands, Renesas has developed a suite of innovative new technologies.

- Chiplet architecture that supports functional safety

To meet the functional safety requirements of automotive SoCs, Renesas has developed a new, proprietary architecture that supports ASIL D even in a chiplet configuration. By combining the standard die-to-die UCIe interface with a proprietary RegionID mechanism, the architecture prevents interference with hardware resources, even when numerous applications run simultaneously, thereby achieving Freedom from Interference (FFI).

Conventional UCIe interfaces lack functionality to transmit RegionIDs between dies. Renesas developed a method for mapping RegionIDs into physical address space, encoding them into the UCIe region, and transmitting them. This enables safe access control through the memory management unit (MMU) and real-time cores, and meets functional safety requirements across chiplets. Additionally, by maintaining bandwidth from processors to the memory bus, the UCIe interface was confirmed through testing to achieve a high transmission speed of 51.2 GB/s, approaching the upper limit of intra-SoC transfer speeds. This technology provides both scalability and safety for high-performance automotive SoCs.

- Advanced AI processing capabilities and automotive-grade quality

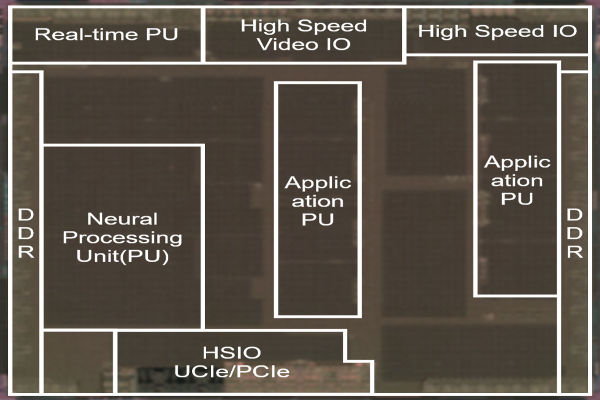

Automotive-grade quality is vital for SDV systems. Renesas has created a 3 nm SoC design that improves the performance of neural processing units (NPUs) for AI processing, while maintaining automotive-grade quality. In recent years, NPUs have been growing larger, with their area expanding 1.5-fold compared to previous generations. This has led to increased clock latency between shared clock sources and individual circuits. To address this problem, Renesas has redesigned the clock architecture by splitting up clock pulse generators (CPGs), which in past designs were module-level units, and placing mini-CPGs (mCPGs) at the sub-module level. This greatly reduces clock latency and meets timing requirements.

However, multi-layer mCPGs complicate test clock synchronization, which is critical for achieving zero defects in automotive applications. Renesas has integrated test circuits into the hierarchical CPG architecture and unified the signal path for user clocks and test clocks. The new design also synchronizes upper- and lower-level mCPGs under a single clock source in test mode. This makes unified phase adjustment possible. As a result, Renesas has been able to achieve quality aligned with zero-defect expectations, even for large-scale SoCs, providing the high reliability required for next-generation SDV automotive SoCs.

- Advanced power control and monitoring for improved power efficiency and safety

To achieve the high level of performance required for automotive SoCs with improved power efficiency and safety, Renesas has developed advanced power gating technology that uses over 90 power domains. It enables precise power control, from several milliwatts to several tens of watts, depending on operating conditions. Furthermore, Renesas has split power switches (PSWs) into ring PSWs and row PSWs to reduce IR drops (voltage drops) associated with increasing current density from smaller process geometries. When power is turned on, the ring PSW suppresses rush currents. Then the row PSW equalizes impedance within the domain. Together, these reduce IR drops by roughly 13% compared with conventional designs.

To meet ASIL D functional safety standards, the dual core lock step (DCLS) configuration controls the master and checker cores with independent power switches and controllers. With this design, even if one side fails, the failure can be detected through lockstep operation. Furthermore, loopback monitoring is performed for each PSW’s gate signal, so OFF states are detected when a failure occurs. A digital voltage meter (DVMON), which is highly resistant to temperature drift, is used for voltage monitoring. This improves aging tolerance by 1.4 mV. These technologies enable high-performance automotive SoCs that offer both power efficiency and safety.

These new technologies are being used in Renesas’ R-Car X5H SoC for automotive multi-domain ECUs. With R-Car X5H, users can accelerate the evolution of SDVs while ensuring safety and enabling autonomous driving, digital cockpit and more.